功率器件模块:一种满足 EMI 规范的捷径时间: 2024-11-27 01:09:33 | 作者: 产品中心 ) 的影响,使其工作过程受到干扰。要确保各电气系统在同一环境中不干扰彼此的正常运行,就必须最大限度地减少辐射。通常,由于硅 (Si) IGBT 和碳化硅 (SiC) MOSFET 等功率半导体器件在工作期间有必要进行快速开关,因此通常会产生传导型 EMI。在开关状态转换过程中,器件两端的电压和流经器件的电流会迅速改变状态。开、关状态间变化会产生 dv/dt 和 di/dt,从而在开关频率的谐波频率上产生 EMI。 图 1:方形、梯形和三角形信号的理论频谱开关频率和边延速率(即器件的状态改变速度)决定了在开关期间产生的 EMI。通常情况下,最高辐射值会出现在开关频率,较低峰值则出现在开关频率的整数倍。例如,如果开关频率为 100 kHz,那么将在 100 kHz、200 kHz、300 kHz 等频率出现辐射频谱峰值。图 1 展示了具有不一样上升时间的脉冲波形在不同频率条件下的频谱辐射衰减情况。对于具有无限 dv/dt 和 di/dt 值的理想方形波,辐射频谱的幅度将以 20 dB/十倍频程的速度递减。对于具有最慢 dv/dt 和 di/dt 的理想三角形波,频谱将下降 40 dB/十倍频程。因此,对于电力电子设备所产生的梯形波,频谱衰减将在 20 dB/十倍频程到 40 dB/十倍频程之间,衰减幅度取决于边延速率。随着器件开关速度加快,谐波频率的辐射频谱预计会增加,而跨频衰减速度将减慢。 这就需要电力电子设计人员在开关频率、边延速率和所产生的 EMI 之间进行一系列权衡。为了更好的提高密度,设计人员可能会选择提高开关频率。这将减少低次谐波,但由于频谱包络向高频移动而可能会引起辐射增加。此外,开关频率升高会增加开关损耗。为了弥补总体损耗的增加,设计人员可能会选择提高边延速率(di/dt 和 dv/dt),以减少开关损耗。遗憾的是,提高边延速率会促进增加系统在更高频率下的辐射。因此,随着在应用场景中提高开关频率和采用高性能、宽禁带器件(如 SiC),设计人员一定考虑 EMI 的影响。

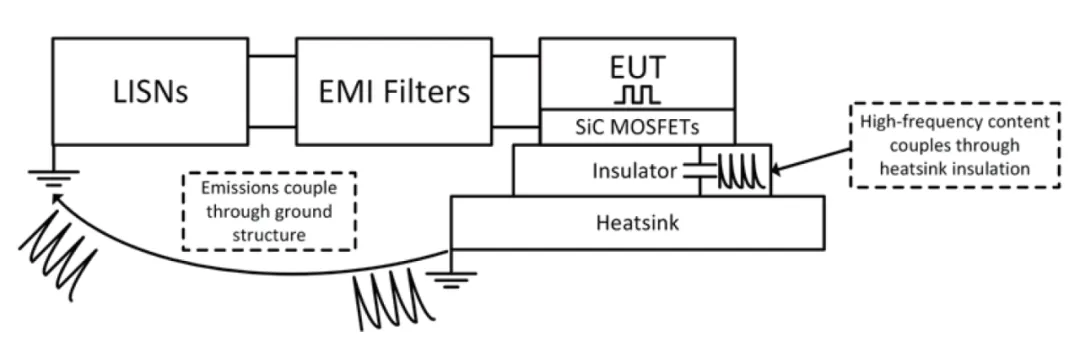

系统的整体辐射不仅取决于电力电子设备的开关行为,而且还取决于所产生的噪声与其他系统的耦合方式。我们的目标是将开关设备产生的频谱含量控制在系统之内,或将辐射移离关键元件。为此,常用方法是在电力电子设备的输入和输出端增加 EMI 滤波器,这些滤波器允许所需频率自由通过,同时重新定向或吸收掉不需要的频率。然而,EMI 滤波器体积大且价格昂贵,因此必须缩小其尺寸以优化成本和功率密度。一种更有效的方法是在设计初期就考虑耦合问题。通过策略性地优化系统内的小的寄生耦合参数,或通过在系统内的寄生耦合周围平衡布置无源元件,可在不使用 EMI 滤波器的情况下大幅减少辐射。这样,设计人员就能通过另一种方法来优化系统并最大限度地减少辐射,同时还能利用碳化硅在提升效率和功率密度方面的优势。不过,这种方法要求设计人员对元件和系统有着深入的了解,但并不总是能直观获取。 寄生电容是电力电子系统中普遍采用的一种重要寄生耦合,位于半导体和散热器之间。通常,会在半导体和散热器之间放置一种电绝缘的导热材料。然而,这实际上是在绝缘体上形成一个小平行板电容,高频共模电流可在此流动,从而提供了向系统辐射的额外路径。图 2 举例说明了这一概念。被测设备 (EUT) 是指完整的变换器或逆变器系统,而线路阻抗稳定网络 (LISN) 是用于 EMC 规范测试的元件,为系统提供已知的输入阻抗。在运行过程中,EUT 产生的高频共模噪声会通过半导体的绝缘电容流向基板,然后流向散热器,再流向 LISN 等其他系统元件。这可能会使频谱辐射升高,从而导致 EUT 无法通过辐射规范测试。这种情况与许多实际系统相吻合,在这些系统中,通常出于安全性和易实施性因素而将散热器接地。因此,在设计应用时一定要考虑这一 CM 噪声路径,以满足规范要求。 与分立式器件相比,功率模块在电气和热特性方面更具优势,可提供更高的功率密度,并且在某些情况下还可简化装配过程。其中一个优势是,使用陶瓷绝缘体将半导体器件的高压导体与模块的金属基板隔开。这样,模块就可以直接连接到接地散热器或其他热管理系统,而无需使用额外的在允许电压下不导电的材料。此外,由于陶瓷特性和厚度受到严控,功率模块对于不同样品具有恒定的电容。因此,模块设计中的电容耦合可以量化,并且独立于所采用的系统。这与分立式器件形成鲜明对比,后者通常使用绝缘硅胶垫,它们: 功率模块具有恒定的耦合值,因此能在功率转换器的设计阶段进行仿真并减少 EMI。对于功率模块,半导体和基板之间的绝缘体电容称为基板电容 (BPC)。

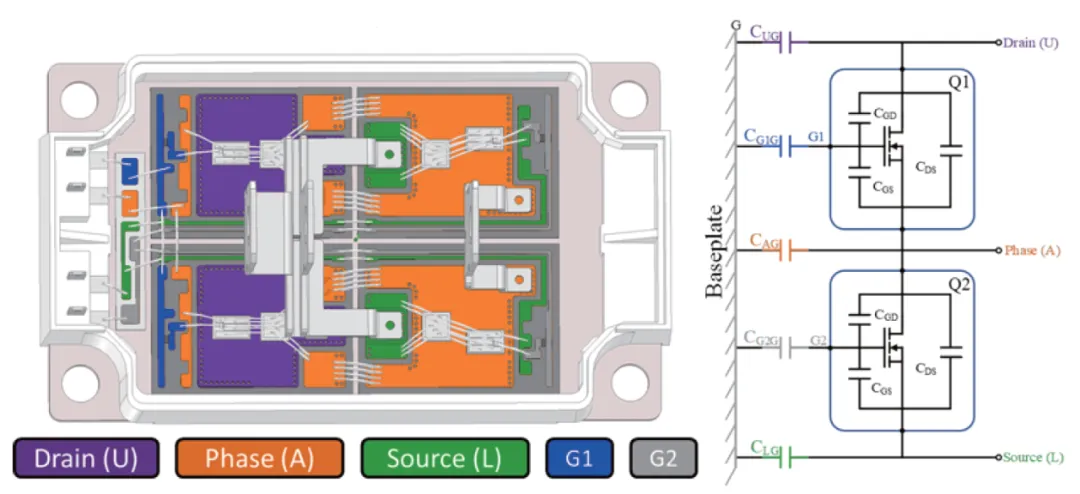

此外,还很有必要了解寄生基板电容分布情况对 EMI 的影响。除各基板电容的总和值外,这些电容之间的比率也对整体共模辐射有着决定性影响。在某些情况下,还可以将这些电容调整为特定的比率,从而在不使用滤波器的情况下大幅度降低共模电流。图 3 举例说明了 Wolfspeed CAS175M12BM3 模块中基板电容的分布情况。通过直连的各基板区域显示为一种颜色,并应将其作为单个集中电容进行建模。由于开尔文源极走线连接到芯片顶部的相应源极引脚,因此它们与源极节点集中在一起。通常,基板区域的面积越大,电容耦合越高。对于半桥模块,完整 BPC 模型包括五个基板电容:每个功率端子一个,每个栅极一个。分离各基板电容的这一逻辑也适用于任何模块拓扑结构。

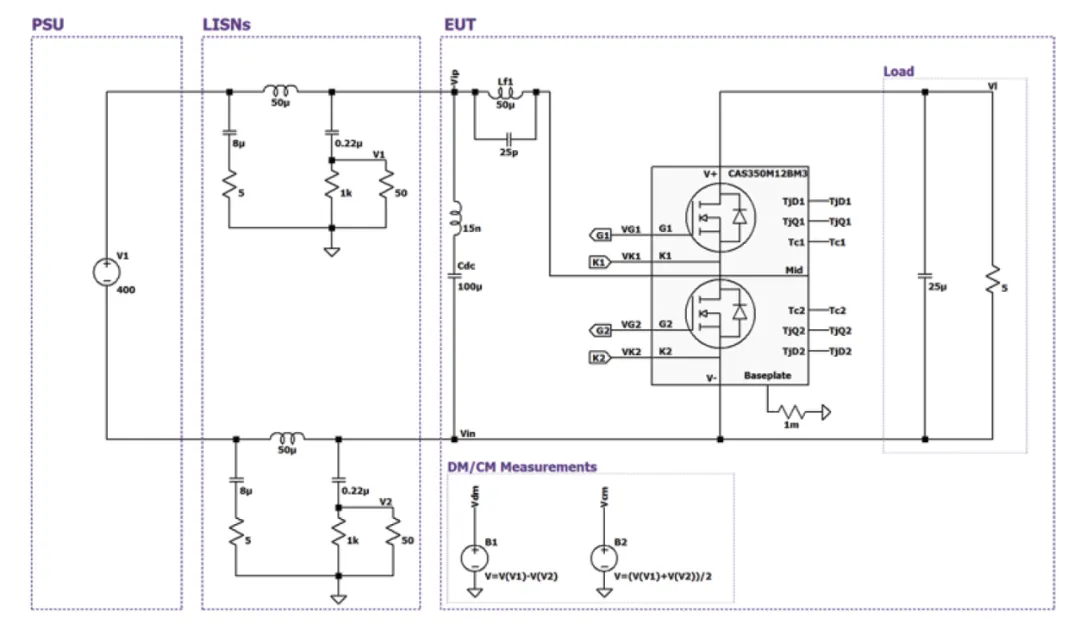

电路级仿真软件(如 LTspice)有助于研究寄生效应和其他参数对 EMI 的影响。Wolfspeed 的功率模块 SPICE 模型在速度和精度方面做了优化,并在封装模型中包含寄生基板电容,因此可有效地用于执行 EMI 仿真。应注意,由于系统和周围环境之间的小的寄生耦合很复杂,因此很难正确预测物理系统的辐射。不过,设计人员可通过仿真来研究寄生元件对辐射的影响,或者试验各种滤波器设计。

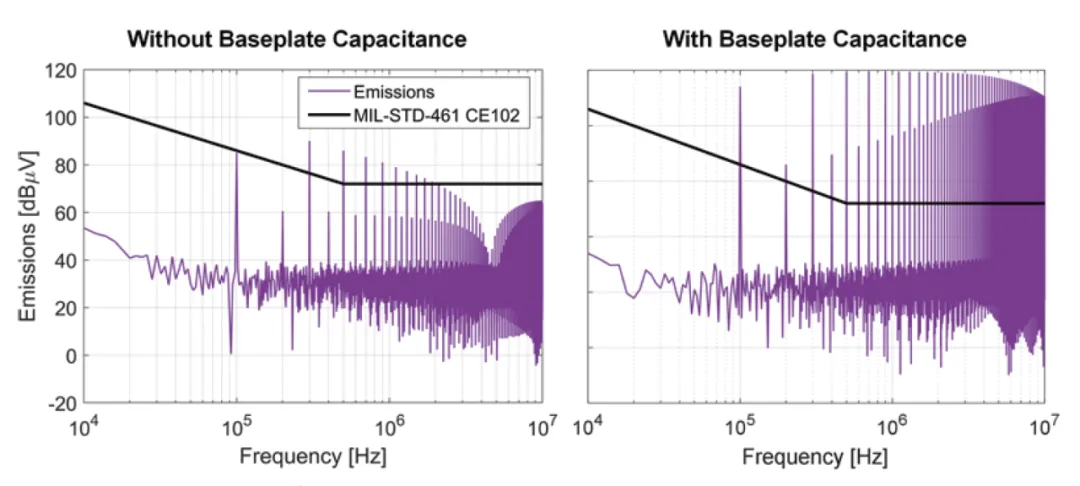

为证明基板电容对 EMI 的影响,在封装模型中含和不含基板电容的情况下评估了图 4 中的 EMC 升压转换器仿真。含基板电容和不含基板电容时 V1 的频谱波形如图 5 所示。图中叠加了 MIL-STD-461 CE102 的辐射限制条件;高于此线的任何频谱含量都表示未满足该标准。虽然在这两种配置条件下系统都不符合 EMC 要求(考虑到未使用 EMI 滤波器,这并不奇怪),但含基板电容的系统在 100 kHz 至 10 MHz 范围内的频谱含量高于辐射谱限制线。而不含基板电容的系统在 2 MHz 以上频率时符合规定标准。应注意,这只是一个理想化示例;在实际系统中,还会有其他共模路径与基板电容并联。 从该方面出发,设计人能利用仿真来应用滤波器、评估寄生耦合的影响、研究共模抑制技术,并进一步了解其系统然后再投入时间和资金进行实证 EMC 规范测试。但是,只有在功率模块的基板电容已知并纳入仿真中的情况下,仿真才有效。Wolfspeed 已对其所有功率模块平台做测量,并公布了相关数据。 Wolfspeed(美国纽约证券交易所上市代码: WOLF)引领碳化硅(SiC)技术在全球市场的采用。我们为高效能源节约和可持续未来提供业界领先的解决方案。Wolfspeed 产品家族包括了 SiC 材料、功率器件,针对电动汽车、快充、可再次生产的能源和储能等多种应用。我们通过勤勉工作、合作以及对于创新的热情,开启更多可能。 |

Copyright © 2020-2023 All Rights Reserved.

备案号:粤ICP备17143418号 网站地图